- 您现在的位置:买卖IC网 > Sheet目录3880 > PIC24F08KL302-I/SO (Microchip Technology)IC MCU 16BIT 8KB FLASH 28-SOIC

CHAPTER 7 16-BIT TIMER/EVENT COUNTERS 0 AND 1

User’s Manual U15905EJ2V1UD

218

(2/2)

The entire TMn unit is asynchronously reset. The supply of clocks to the

TMn unit stops.

Clocks are supplied to the TMn unit.

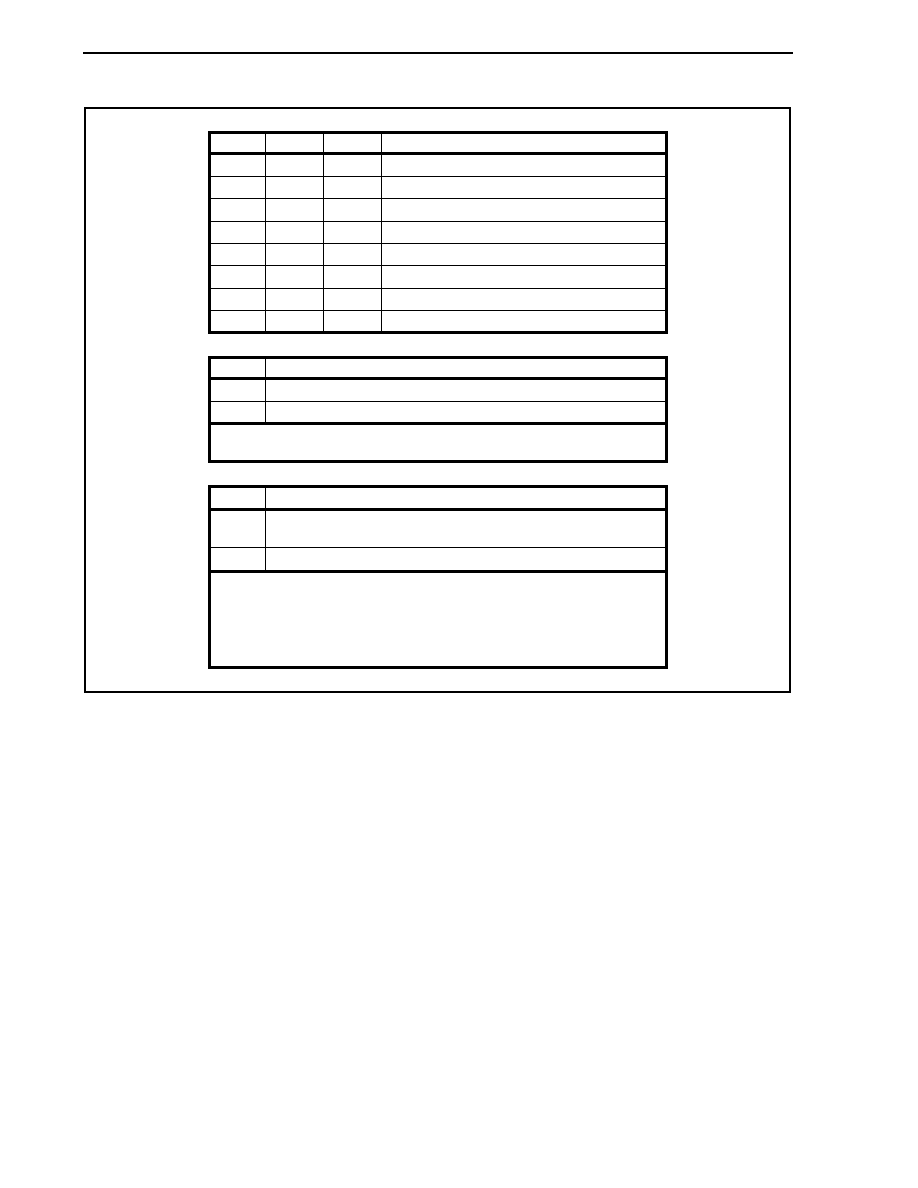

TMCAEn

0

Internal count clock control

fXX/2

fXX/4

fXX/8

fXX/16

fXX/32

fXX/64

fXX/128

fXX/256

CSn2

0

1

Internal count clock selection

CSn1

0

1

0

1

CSn0

0

1

0

1

0

1

0

1

Count disabled (stops at 0000H and does not operate).

Counting operation is performed.

TMCEn

0

1

TMn register operation control

When TMCEn = 0, the external pulse output (TOn) becomes inactive (the active

level of TOn output is set by the ALVn bit of the TMCn1 register).

When the TMCAEn bit is set to 0, the TMn unit can be asynchronously reset.

When TMCAEn = 0, the TMn unit is in a reset state. Therefore, to operate TMn,

the TMCAEn bit must be set to 1.

When the TMCAEn bit is changed from 1 to 0, all registers of the TMn unit are

initialized. When TMCAEn is set to 1 again, the TMn unit registers must be set

again.

1

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XF2L-0535-1

CONN FPC 5POS 0.5MM SMT

PIC18LF23K22-I/SS

IC PIC MCU 8KB FLASH 28SSOP

PIC16LF1933-I/ML

IC PIC MCU FLASH 4K 28-QFN

PIC16F1933-I/ML

IC MCU 8BIT FLASH 28-QFN

PIC16F785-I/ML

IC PIC MCU FLASH 2KX14 20QFN

XF2L-0425-1

CONN FPC 4POS 0.5MM SMT

PIC16F1933-I/MV

IC MCU 8BIT FLASH 28-UQFN

PIC16F785-I/SO

IC PIC MCU FLASH 2KX14 20SOIC

相关代理商/技术参数

PIC24F08KL302-I/SP

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302-I/SS

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/ML

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/MQ

功能描述:16位微控制器 - MCU 8KB FL 1KB RAM 256B 3V RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/SO

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL302T-I/SS

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT

PIC24F08KL401

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:Low-Power, Low-Cost, General Purpose 16-Bit Flash Microcontrollers with nanoWatt XLP Technology

PIC24F08KL401-I/MQ

功能描述:16位微控制器 - MCU 8KB FLASH 1KB RAM 512B 3V 10-BIT ADC RoHS:否 制造商:Texas Instruments 核心:RISC 处理器系列:MSP430FR572x 数据总线宽度:16 bit 最大时钟频率:24 MHz 程序存储器大小:8 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:2 V to 3.6 V 工作温度范围:- 40 C to + 85 C 封装 / 箱体:VQFN-40 安装风格:SMD/SMT